# Current status of external test pulse equalization

### Introduction

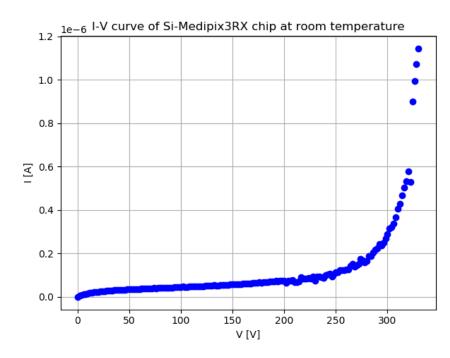

#### IV Curve

#### Chip in study

| Type       | Wafer   | ID       |

|------------|---------|----------|

| Medipix3RX | Silicon | 7FB1FE72 |

#### External test pulses

Type of pulses:

Amplitude= 0.1, 0.2, 0.3, 0.4, 0.5, 1, 2, 3 V

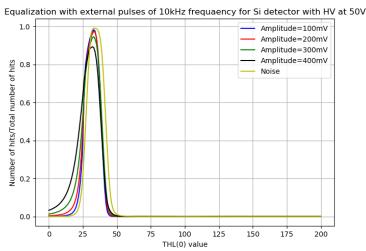

## External test pulses

#### Variation of the amplitude:

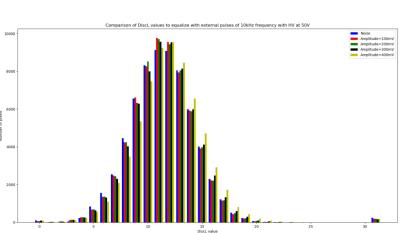

## External test pulses

#### Variation of the amplitude:

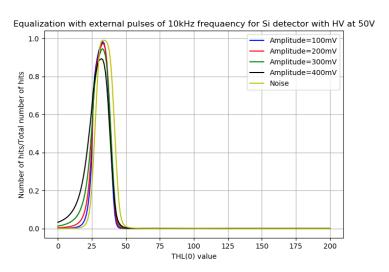

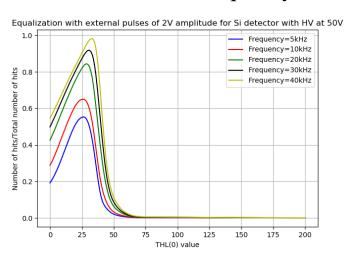

#### Variation of the frequency:

## External test pulses: Problems

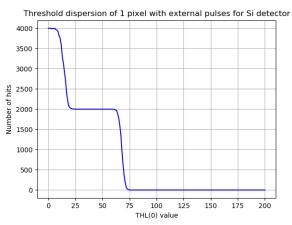

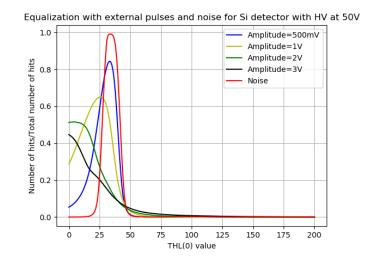

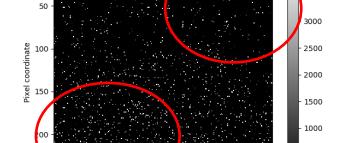

#### Acquisition with noise

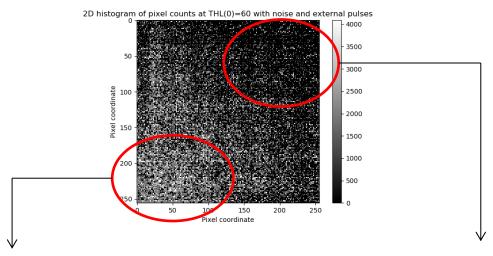

## 2D histogram of pixel counts at THL(0)=60 where noise is the only signal 4000 3500 3000

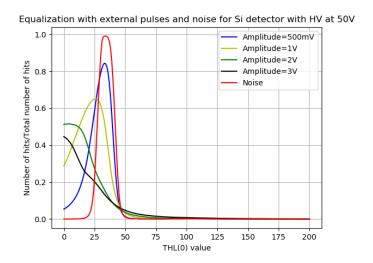

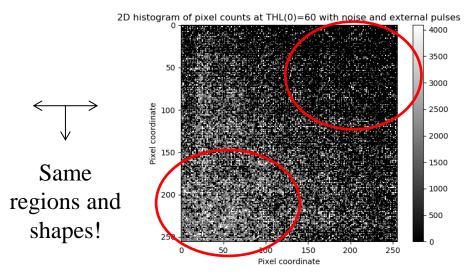

#### Acquisition with external pulses and noise

The problems may come from:

200

- Chip

- Injection of the pulses

Pixel coordinate

(difference in the bump bonds, ...)

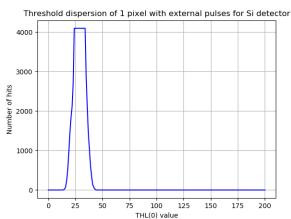

## External test pulses: Problems

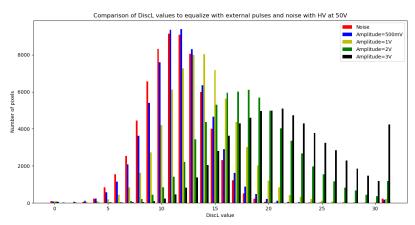

#### Acquisition with external pulses and noise